# **CORE-V-Docs Documentation**

**Davide Schiavone**

Feb 16, 2022

# CONTENTS:

| 1 | Changelog           1.1         0.1.0                                                                                                                                      | <b>3</b><br>3                                     |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 2 | Introduction2.1License2.2Standards Compliance2.3Synthesis guidelines2.3.1ASIC Synthesis2.3.2FPGA Synthesis2.4Verification2.5Contents2.6History2.7References2.8Contributors | <b>5</b><br>6<br>8<br>8<br>9<br>9<br>9<br>9<br>10 |

| 3 |                                                                                                                                                                            | <b>11</b><br>11                                   |

| 4 | 4.1       Instantiation Template         4.2       Parameters                                                                                                              | <b>13</b><br>13<br>15<br>17                       |

| 5 | 5.1 Multi- and Single-Cycle Instructions                                                                                                                                   | <b>19</b><br>19<br>21                             |

| 6 | 6.1 Misaligned Accesses                                                                                                                                                    | <b>23</b><br>24<br>24                             |

| 7 | 7.1       Misaligned Accesses       7.2         Protocol       7.2                                                                                                         | <b>27</b><br>28<br>28<br>29                       |

| 8 | 8.1       Address range         8.2       Main memory vs I/O         8.3       Bufferable and Cacheable                                                                    | <b>31</b><br>31<br>31<br>32<br>32                 |

|    | 8.5   | Default          | attribution                                                                                                    |

|----|-------|------------------|----------------------------------------------------------------------------------------------------------------|

| 9  | Regis | ster File        | 33                                                                                                             |

|    | 9.1   |                  | Purpose Register File         33                                                                               |

| 10 | oVtor | nsion Int        | erface 35                                                                                                      |

| 10 |       |                  | V-XIF                                                                                                          |

|    | 10.1  | 10.1.1           | Compressed interface                                                                                           |

|    |       | 10.1.2           | Issue interface                                                                                                |

|    |       | 10.1.3           | Commit interface                                                                                               |

|    |       | 10.1.4           | Memory (request/response) interface                                                                            |

|    |       | 10.1.5           | Memory result interface                                                                                        |

|    |       | 10.1.6           | Result interface                                                                                               |

|    | 10.2  | 0                | ion                                                                                                            |

|    | 10.3  | Timing           |                                                                                                                |

| 11 | Fence | e.i extern       | al handshake 41                                                                                                |

| 10 | CI    | <b>T</b> T •4    | 40                                                                                                             |

| 12 | Sleep |                  | <b>43</b> behavior                                                                                             |

|    |       |                  | behavior         43           44         44                                                                    |

|    | 12.2  | WГI              |                                                                                                                |

| 13 |       |                  | Status Registers 45                                                                                            |

|    |       |                  | ap                                                                                                             |

|    | 13.2  |                  | 47 47 47                                                                                                       |

|    |       | 13.2.1           | Jump Vector Table (jvt)                                                                                        |

|    |       | 13.2.2           | Machine Status (mstatus)       48         Machine ISA (miga)       40                                          |

|    |       | 13.2.3<br>13.2.4 | Machine ISA (misa)       49         Machine Interrupt Enable Register (mie) - SMCLIC == 0       50             |

|    |       | 13.2.4           | Machine Interrupt Enable Register (mie) - SMCLIC == 050Machine Interrupt Enable Register (mie) - SMCLIC == 150 |

|    |       | 13.2.6           | Machine Trap-Vector Base Address (mtvec) - SMCLIC == 0                                                         |

|    |       | 13.2.7           | Machine Trap-Vector Base Address (mtvec) - SMCLIC == 1                                                         |

|    |       | 13.2.8           | Machine Trap Vector Table Base Address (mtvt)                                                                  |

|    |       | 13.2.9           | Machine Status (mstatush)                                                                                      |

|    |       | 13.2.10          | Machine Counter-Inhibit Register (mcountinhibit) 52                                                            |

|    |       | 13.2.11          | Machine Performance Monitoring Event Selector (mhpmevent3 mhpmevent31) 52                                      |

|    |       | 13.2.12          | Machine Scratch (mscratch)                                                                                     |

|    |       |                  | Machine Exception PC (mepc)                                                                                    |

|    |       |                  | Machine Cause (mcause) - SMCLIC == $0$                                                                         |

|    |       |                  | Machine Cause (mcause) - SMCLIC == 1                                                                           |

|    |       |                  | Machine Trap Value (mtval)                                                                                     |

|    |       |                  | Machine Interrupt Pending Register (mip) - SMCLIC == 0                                                         |

|    |       |                  | Machine Interrupt Pending Register (mip) - SMCLIC == 1                                                         |

|    |       |                  | Machine Next Interrupt Handler Address and Interrupt Enable (mnxti)55Machine Interrupt Status (mintstatus)56   |

|    |       |                  | Machine Interrupt-Level Threshold (mintthresh)                                                                 |

|    |       |                  | Machine Scratch Swap for Priv Mode Change (mscratchcsw)                                                        |

|    |       |                  | Machine Scratch Swap for Interrupt-Level Change (mscratchcswl)                                                 |

|    |       |                  | CLIC Base (mclicbase)                                                                                          |

|    |       |                  | Trigger Select Register (tselect)                                                                              |

|    |       |                  | Trigger Data 1 (tdata1)         58                                                                             |

|    |       |                  | Match Control Type 6 (mcontrol6) 58                                                                            |

|    |       |                  | Exception Trigger (etrigger)                                                                                   |

|    |       |                  | Trigger Data Register 2 (tdata2)    60                                                                         |

|    |       | 13.2.30          | Trigger Data Register 3 (tdata3)    60                                                                         |

|    |                                                                                                                                                                                                                         | 13.2.31 Trigger Info (tinfo)13.2.32 Trigger Control (tcontrol)13.2.33 Machine Context Register (mcontext)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61<br>61<br>61                                                                                                                    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                                                         | 13.2.34 Machine Supervisor Context Register (mscontext)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.35 Debug Control and Status (dcsr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.36 Debug PC (dpc)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.37 Debug Scratch Register 0/1 (dscratch0/1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.38 Machine Cycle Counter (mcycle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.39 Machine Instructions-Retired Counter (minstret)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.40 Machine Performance Monitoring Counter (mhpmcounter3 mhpmcounter31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 64                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.41 Upper 32 Machine Cycle Counter (mcycleh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                                                                                |

|    |                                                                                                                                                                                                                         | <ul><li>13.2.42 Upper 32 Machine Instructions-Retired Counter (minstreth)</li><li>13.2.43 Upper 32 Machine Performance Monitoring Counter (mhpmcounter3h mhpmcounter31h)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.44 Machine Vendor ID (mvendorid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.45 Machine Architecture ID (marchid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 65                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.46 Machine Implementation ID (mimpid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.47 Hardware Thread ID (mhartid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.48 Machine Configuration Pointer (mconfigptr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.49 Cycle Counter (cycle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.50 Instructions-Retired Counter (instret)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.51 Performance Monitoring Counter (hpmcounter3 hpmcounter31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.52 Upper 32 Cycle Counter (cycleh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                                                                                                                |

|    |                                                                                                                                                                                                                         | 13.2.53 Upper 32 Instructions-Retired Counter (instreth)13.2.54 Upper 32 Performance Monitoring Counter (hpmcounter3h hpmcounter31h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67<br>67                                                                                                                          |

|    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 07                                                                                                                                |

| 14 |                                                                                                                                                                                                                         | ormance Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>69</b>                                                                                                                         |

|    |                                                                                                                                                                                                                         | Event Selector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                                                |

|    | 14.2                                                                                                                                                                                                                    | Controlling the counters from software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70                                                                                                                                |

|    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|    | 14.3                                                                                                                                                                                                                    | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                                                                                                                                |

|    | 14.3                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| 15 | 14.3<br>14.4<br>Exce                                                                                                                                                                                                    | Parametrization at synthesis time<br>Time Registers (time(h))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                                                                                                |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1                                                                                                                                                                                     | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br><b>71</b><br>71                                                                                                       |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2                                                                                                                                                                             | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br><b>71</b><br>71<br>72                                                                                                 |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3                                                                                                                                                                     | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br><b>71</b><br>71<br>72<br>73                                                                                           |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4                                                                                                                                                             | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br><b>71</b><br>71<br>72<br>73<br>73                                                                                     |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5                                                                                                                                                     | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br>71<br>71<br>72<br>73<br>73<br>73                                                                                      |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6                                                                                                                                             | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupts - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70<br>70<br>71<br>71<br>72<br>73<br>73<br>73<br>73<br>74                                                                          |

| 15 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6                                                                                                                                             | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70<br>70<br>71<br>71<br>72<br>73<br>73<br>73                                                                                      |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> </ul>                                           | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70<br>70<br>71<br>71<br>72<br>73<br>73<br>73<br>73<br>74                                                                          |

|    | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br><b>Debu</b><br>16.1                                                                                                              | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70<br>70<br><b>71</b><br>71<br>72<br>73<br>73<br>73<br>73<br>74<br>75                                                             |

|    | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br><b>Debu</b><br>16.1<br>16.2                                                                                                      | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70<br>70<br>71<br>71<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>74<br>75<br>77<br>78<br>78<br>78              |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> <li>16.1</li> <li>16.2</li> <li>16.3</li> </ul> | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupts - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 700<br>700<br>711<br>712<br>733<br>733<br>733<br>733<br>743<br>755<br>776<br>778<br>788<br>788<br>79                              |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> <li>16.1</li> <li>16.2</li> <li>16.3</li> </ul> | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 700<br>700<br>711<br>722<br>733<br>733<br>733<br>733<br>733<br>744<br>755<br>777<br>788<br>789<br>799<br>79                       |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> <li>16.1</li> <li>16.2</li> <li>16.3</li> </ul> | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state         Interface         Interface         Interface         Interface         Interface         Interface         Interface         Interface         Debug state         Interface         Interface | 700<br>700<br>711<br>722<br>733<br>733<br>744<br>755<br>774<br>758<br>787<br>788<br>788<br>799<br>799<br>799                      |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> <li>16.1</li> <li>16.2</li> <li>16.3</li> </ul> | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 700<br>701<br>711<br>722<br>733<br>733<br>733<br>733<br>743<br>755<br>777<br>788<br>788<br>789<br>799<br>799<br>800               |

|    | <ul> <li>14.3</li> <li>14.4</li> <li>Exception</li> <li>15.1</li> <li>15.2</li> <li>15.3</li> <li>15.4</li> <li>15.5</li> <li>15.6</li> <li>15.7</li> <li>Debution</li> <li>16.1</li> <li>16.2</li> <li>16.3</li> </ul> | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state         Interface         Interface         Interface         Interface         Interface         Interface         Interface         Interface         Debug state         Interface         Interface | 700<br>700<br>711<br>722<br>733<br>733<br>744<br>755<br>774<br>758<br>787<br>788<br>788<br>799<br>799<br>799                      |

| 16 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br><b>Debu</b><br>16.1<br>16.2<br>16.3<br>16.4                                                                                      | Parametrization at synthesis time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 700<br>701<br>711<br>722<br>733<br>733<br>733<br>733<br>743<br>755<br>777<br>788<br>788<br>789<br>799<br>799<br>800               |

| 16 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br><b>Debu</b><br>16.1<br>16.2<br>16.3<br>16.4                                                                                      | Parametrization at synthesis time         Time Registers (time (h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state         IBREAK Behavior         16.4.1 Scenario 1: Enter Exception         16.4.3 Scenario 3: Exit Program Buffer & Restart Debug Code                                                                                                                                                                                                                                                                                                                                                           | 700<br>700<br>711<br>712<br>733<br>733<br>733<br>733<br>733<br>743<br>755<br>776<br>788<br>799<br>799<br>799<br>799<br>800<br>800 |

| 16 | 14.3<br>14.4<br><b>Exce</b><br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br><b>Debu</b><br>16.1<br>16.2<br>16.3<br>16.4<br><b>RISC</b>                                                                       | Parametrization at synthesis time         Time Registers (time (h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupt - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state         EBREAK Behavior         16.4.1       Scenario 1: Enter Exception         16.4.3       Scenario 3: Exit Program Buffer & Restart Debug Code                                                                                                                                                                                                                                                                                                                                                         | 700<br>700<br>711<br>712<br>733<br>733<br>743<br>755<br>777<br>788<br>788<br>788<br>799<br>799<br>799<br>799<br>800<br>800<br>801 |

| 16 | 14.3<br>14.4<br>Excep<br>15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br>Debu<br>16.1<br>16.2<br>16.3<br>16.4<br>RISC<br>17.1                                                                                   | Parametrization at synthesis time         Time Registers (time(h))         ptions and Interrupts         Interrupt Interface - SMCLIC == 0         Interrupts - SMCLIC == 0         Interrupt Interface - SMCLIC == 1         Interrupts - SMCLIC == 1         Non Maskable Interrupts         Exceptions         Nested Interrupt/Exception Handling         Interface         Core Debug Registers         Debug state         Indering 1: Enter Exception         16.4.1       Scenario 1: Enter Debug Mode         16.4.3       Scenario 3: Exit Program Buffer & Restart Debug Code         C-V Formal Interface         New Additions                                                                                                                                                                                                                                                                                                                          | 700<br>700<br>711<br>712<br>733<br>733<br>733<br>744<br>755<br>777<br>788<br>789<br>799<br>799<br>799<br>800<br>800<br>811<br>811 |

#### 18 CORE-V Instruction Set Extensions

| 19 | Core  | Version | s and RTL Freeze Rules                     | 89 |

|----|-------|---------|--------------------------------------------|----|

|    | 19.1  | What ha | appens after RTL Freeze?                   | 89 |

|    |       | 19.1.1  | A bug is found                             | 89 |

|    |       | 19.1.2  | RTL changes on non-verified yet parameters | 89 |

|    |       | 19.1.3  | PPA optimizations and new features         | 89 |

|    | 19.2  | Release | d core versions                            | 90 |

| 20 | Gloss | ary     |                                            | 91 |

87

93

| Diblia | anonhi | 7 |

|--------|--------|---|

| DIDIIO | graphy | / |

iv

Editor: Davide Schiavone davide@openhwgroup.org

### ONE

# CHANGELOG

### 1.1 0.1.0

Released on 2022-02-16 - GitHub

TWO

# INTRODUCTION

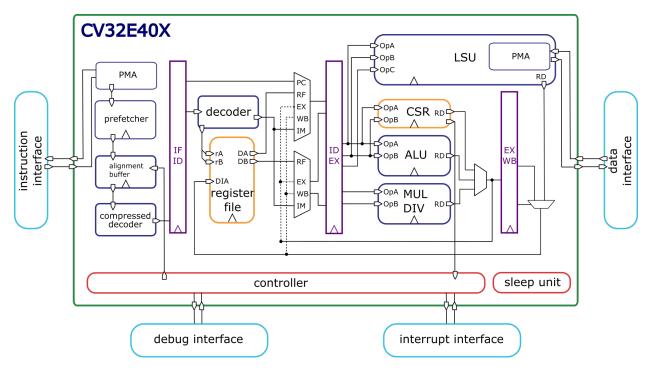

CV32E40X is a 4-stage in-order 32-bit RISC-V processor core. Figure 2.1 shows a block diagram of the core.

Figure 2.1: Block Diagram of CV32E40X RISC-V Core

# 2.1 License

Copyright 2020 OpenHW Group.

Copyright 2018 ETH Zurich and University of Bologna.

Copyright and related rights are licensed under the Solderpad Hardware License, Version 0.51 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at http://solderpad. org/licenses/SHL-0.51. Unless required by applicable law or agreed to in writing, software, hardware and materials distributed under this License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

# 2.2 Standards Compliance

CV32E40X is a standards-compliant 32-bit RISC-V processor. It follows these specifications:

Many features in the RISC-V specification are optional, and CV32E40X can be parameterized to enable or disable some of them.

CV32E40X supports one of the following base integer instruction sets from [RISC-V-UNPRIV].

| Base Integer Instruction Set                      | Version                | Configurability                            |

|---------------------------------------------------|------------------------|--------------------------------------------|

| RV32I: RV32I Base Integer Instruction Set         | 2.1                    | optionally enabled with the RV32 parameter |

| <b>RV32E</b> : RV32E Base Integer Instruction Set | 1.9 (not ratified yet) | optionally enabled with the RV32 parameter |

Table 2.1: CV32E40X Base Instruction Set

In addition, the following standard instruction set extensions are available from [RISC-V-UNPRIV], [RISC-V-ZBA\_ZBB\_ZBC\_ZBS], [RISC-V-CRYPTO] and [RISC-V-ZCA\_ZCB\_ZCMB\_ZCMP\_ZCMT].

| Standard Extension                                                    | Version               | Configurability    |

|-----------------------------------------------------------------------|-----------------------|--------------------|

| C: Standard Extension for Compressed Instructions                     | 2.0                   | always enabled     |

| M: Standard Extension for Integer Multiplication and Division         | 2.0                   | optionally enabled |

|                                                                       |                       | with the M_EXT     |

|                                                                       |                       | parameter          |

| Zicntr: Standard Extension for Base Counters and Timers               | 2.0                   | always enabled     |

| Zihpm: Standard Extension for Hardware Performance Counters           | 2.0                   | always enabled     |

| Zicsr: Control and Status Register Instructions                       | 2.0                   | always enabled     |

| Zifencei: Instruction-Fetch Fence                                     | 2.0                   | always enabled     |

| Zca: Subset of the standard Zc Code-Size Reduction extension          | v0.70.1 (not ratified | optionally enabled |

| consisting of a subset of C with the FP load/stores removed.          | yet; version will     | with the ZC_EXT    |

|                                                                       | change)               | parameter          |

| Zcb: Subset of the standard Zc Code-Size Reduction extension          | v0.70.1 (not ratified | optionally enabled |

| consisting of simple operations.                                      | yet; version will     | with the ZC_EXT    |

|                                                                       | change)               | parameter          |

| Zcmb: Subset of the standard Zc Code-Size Reduction extension         | v0.70.1 (not ratified | optionally enabled |

| consisting of load/store byte/half which overlap with c.fld, c.fldsp, | yet; version will     | with the ZC_EXT    |

| c.fsd.                                                                | change)               | parameter          |

| Zcmp: Subset of the standard Zc Code-Size Reduction exten-            | v0.70.1 (not ratified | optionally enabled |

| sion consisting of push/pop and double move which overlap with        | yet; version will     | with the ZC_EXT    |

| c.fsdsp.                                                              | change)               | parameter          |

| Zcmt: Subset of the standard Zc Code-Size Reduction extension         | v0.70.1 (not ratified | optionally enabled |

| consisting of table jump.                                             | yet; version will     | with the ZC_EXT    |

|                                                                       | change)               | parameter          |

| A: Atomic Instructions                                                | 2.1                   | optionally enabled |

|                                                                       |                       | with the A_EXT     |

|                                                                       |                       | parameter          |

| Zba: Bit Manipulation Address calculation instructions                | Version 1.0.0         | optionally enabled |

|                                                                       |                       | with the B_EXT     |

|                                                                       |                       | parameter          |

| <b>Zbb</b> : Bit Manipulation Base instructions                       | Version 1.0.0         | optionally enabled |

|                                                                       |                       | with the B_EXT     |

|                                                                       |                       | parameter          |

| Zbc: Bit Manipulation Carry-Less Multiply instructions                | Version 1.0.0         | optionally enabled |

|                                                                       |                       | with the B_EXT     |

|                                                                       |                       | parameter          |

| Zbs: Bit Manipulation Bit set, Bit clear, etc. instructions           | Version 1.0.0         | optionally enabled |

|                                                                       |                       | with the B_EXT     |

|                                                                       |                       | parameter          |

| Zkt: Data Independent Execution Latency                               | Version 1.0.0         | always enabled     |

| Zbkc: Constant time Carry-Less Multiply                               | Version 1.0.0         | optionally enabled |

|                                                                       |                       | with the B_EXT     |

|                                                                       |                       | parameter          |

| Zmmul: Multiplication subset of the M extension                       | Version 0.1           | optionally enabled |