Introduction

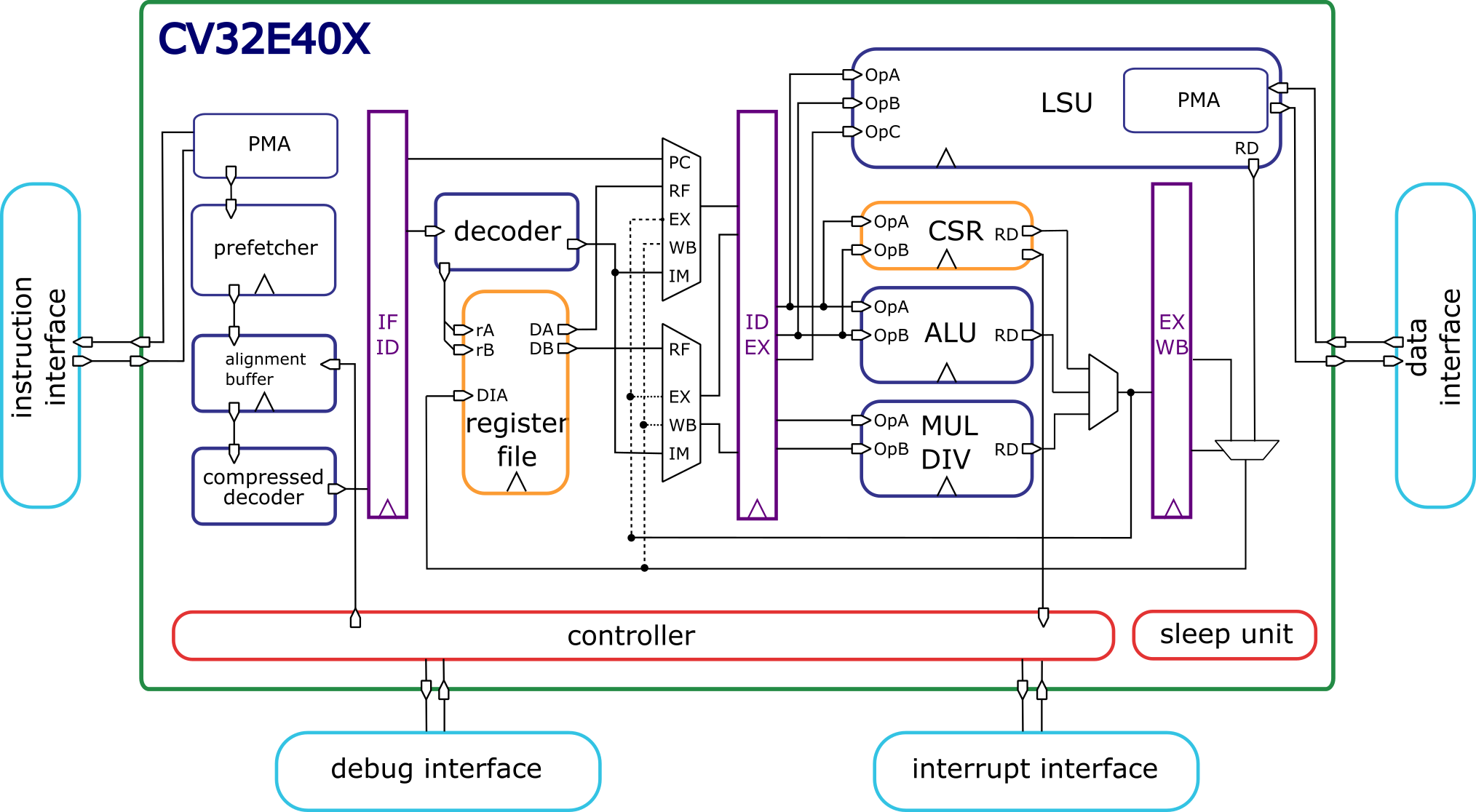

CV32E40X is a 4-stage in-order 32-bit RISC-V processor core. Figure 1 shows a block diagram of the core.

Figure 1 Block Diagram of CV32E40X RISC-V Core

License

Copyright 2020 OpenHW Group.

Copyright 2018 ETH Zurich and University of Bologna.

Copyright and related rights are licensed under the Solderpad Hardware License, Version 0.51 (the “License”); you may not use this file except in compliance with the License. You may obtain a copy of the License at http://solderpad.org/licenses/SHL-0.51. Unless required by applicable law or agreed to in writing, software, hardware and materials distributed under this License is distributed on an “AS IS” BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Standards Compliance

CV32E40X is a standards-compliant 32-bit RISC-V processor. It follows these specifications:

RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 20191213 (December 13, 2019), https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf

RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Document Version 20211203 (December 4, 2021), https://github.com/riscv/riscv-isa-manual/releases/download/Priv-v1.12/riscv-privileged-20211203.pdf

RISC-V Instruction Set Manual, Volume I: User-Level ISA, RV32E Base Integer Instruction Set, Document version 20191214-draft (January 31, 2023), https://github.com/riscv/riscv-isa-manual/releases/download/draft-20230131-c0b298a/riscv-spec.pdf

RISC-V Debug Support, version 1.0-STABLE, f5b2ed3bb0eefcca075e99f3a8eece06e8d60063, October 12 2023, https://github.com/riscv/riscv-debug-spec/blob/51f5a29c0126d69f314079fb4f1197876aca7622/riscv-debug-stable.pdf

Core-Local Interrupt Controller (CLIC) RISC-V Privileged Architecture Extensions, version 0.9-draft, 9/1/2023, https://github.com/riscv/riscv-fast-interrupt/blob/894a16ce89dcf2c084dd951866448c2e756d3efa/clic.pdf

RISC-V Bit Manipulation ISA-extensions, Version 1.0.0-38-g865e7a7, 2021-06-28, https://github.com/riscv/riscv-bitmanip/releases/download/1.0.0/bitmanip-1.0.0-38-g865e7a7.pdf

RISC-V Standard Extension for the Zca, Zcb, Zcmp, Zcmt subsets of Zc, v1.0.0-RC5.7 (not ratified yet), https://github.com/riscv/riscv-code-size-reduction/releases/download/v1.0.0-RC5.7/Zc-v1.0.0-RC5.7.pdf

RISC-V Cryptography Extensions Volume I, Scalar & Entropy Source Instructions, Version v1.0.0, 2’nd December, 2021: Ratified, https://github.com/riscv/riscv-crypto/releases/download/v1.0.0-scalar/riscv-crypto-spec-scalar-v1.0.0.pdf

OpenHW Open Bus Interface (OBI) protocol, version 1.6.0, https://github.com/openhwgroup/obi/blob/072d9173c1f2d79471d6f2a10eae59ee387d4c6f/OBI-v1.6.0.pdf

OpenHW eXtension Interface, revision 458c8a73, https://docs.openhwgroup.org/projects/openhw-group-core-v-xif/

Symbiotic EDA RISC-V Formal Interface https://github.com/SymbioticEDA/riscv-formal/blob/master/docs/rvfi.md

Many features in the RISC-V specification are optional, and CV32E40X can be parameterized to enable or disable some of them.

CV32E40X supports one of the following base integer instruction sets:

Base Integer Instruction Set |

Version |

Configurability |

|---|---|---|

RV32I: RV32I Base Integer Instruction Set |

2.1 (from [RISC-V-UNPRIV]) |

optionally enabled with the |

RV32E: RV32E Base Integer Instruction Set |

2.0 (from [RISC-V-RV32E]) |

optionally enabled with the |

In addition, the following standard instruction set extensions are available from [RISC-V-UNPRIV], [RISC-V-ZBA_ZBB_ZBC_ZBS], [RISC-V-CRYPTO] and [RISC-V-ZCA_ZCB_ZCMP_ZCMT].

Standard Extension |

Version |

Configurability |

|---|---|---|

C: Standard Extension for Compressed Instructions |

2.0 |

always enabled |

M: Standard Extension for Integer Multiplication and Division |

2.0 |

optionally enabled with the |

Zicntr: Standard Extension for Base Counters and Timers |

2.0 |

always enabled |

Zihpm: Standard Extension for Hardware Performance Counters |

2.0 |

always enabled |

Zicsr: Control and Status Register Instructions |

2.0 |

always enabled |

Zifencei: Instruction-Fetch Fence |

2.0 |

always enabled |

Zca: Subset of the standard Zc Code-Size Reduction extension consisting of a subset of C with the FP load/stores removed. |

v1.0.0-RC5.6 (not ratified yet; version will change) |

always enabled |

Zcb: Subset of the standard Zc Code-Size Reduction extension consisting of simple operations. |

v1.0.0-RC5.6 (not ratified yet; version will change) |

always enabled |

Zcmp: Subset of the standard Zc Code-Size Reduction extension consisting of push/pop and double move which overlap with c.fsdsp. |

v1.0.0-RC5.6 (not ratified yet; version will change) |

always enabled |

Zcmt: Subset of the standard Zc Code-Size Reduction extension consisting of table jump. |

v1.0.0-RC5.6 (not ratified yet; version will change) |

always enabled |

A: Atomic Instructions |

2.1 |

optionally enabled with the |

Zba: Bit Manipulation Address calculation instructions |

Version 1.0.0 |

optionally enabled with the |

Zbb: Bit Manipulation Base instructions |

Version 1.0.0 |

optionally enabled with the |

Zbc: Bit Manipulation Carry-Less Multiply instructions |

Version 1.0.0 |

optionally enabled with the |

Zbs: Bit Manipulation Bit set, Bit clear, etc. instructions |

Version 1.0.0 |

optionally enabled with the |

Zkt: Data Independent Execution Latency |

Version 1.0.0 |

always enabled |

Zbkc: Constant time Carry-Less Multiply |

Version 1.0.0 |

optionally enabled with the |

Zmmul: Multiplication subset of the M extension |

Version 0.1 |

optionally enabled with the |

The following custom instruction set extensions are available.

Custom Extension |

Version |

Configurability |

|---|---|---|

Xif: eXtension Interface |

0.1 (not finalized yet; version will change) |

optionally enabled with the |

Note

CV32E40X does not implement the F extension for single-precision floating-point instructions internal to the core. The F extension can be supported by interfacing the CV32E40X to an external FPU via the eXtension interface.

Most content of the RISC-V privileged specification is optional. CV32E40X supports the following features according to the RISC-V Privileged Specification [RISC-V-PRIV]:

M-Mode

All CSRs listed in Control and Status Registers

Base Counters, Timers and Hardware Performance Counters as described in Performance Counters controlled by the

NUM_MHPMCOUNTERSparameterTrap handling supporting direct mode or vectored mode as described at Exceptions and Interrupts

Physical Memory Attribution (PMA) as described in Physical Memory Attribution (PMA)

CV32E40X supports the following ISA extensions from the RISC-V Debug Support specification [RISC-V-DEBUG]:

Sdext: External Debug support. Optionally enabled with the

DEBUGparameter.Sdtrig: Trigger Module. Optionally enabled with the

DBG_NUM_TRIGGERSparameter.

Synthesis guidelines

The CV32E40X core is fully synthesizable. It has been designed mainly for ASIC designs, but FPGA synthesis is supported as well.

All the files in the rtl and rtl/include folders are synthesizable. The top level module is called cv32e40x_core.

The user must provide a clock-gating module that instantiates

the clock-gating cells of the target technology. This file must have the same interface and module name of the one provided for simulation-only purposes

at bhv/cv32e40x_sim_clock_gate.sv (see Clock Gating Cell).

The constraints/cv32e40x_core.sdc file provides an example of synthesis constraints. No synthesis scripts are provided.

ASIC Synthesis

ASIC synthesis is supported for CV32E40X. The whole design is completely synchronous and uses positive-edge triggered flip-flops. A technology specific implementation of a clock gating cell as described in Clock Gating Cell needs to be provided.

FPGA Synthesis

FPGA synthesis is supported for CV32E40X. The user needs to provide a technology specific implementation of a clock gating cell as described in Clock Gating Cell.

Verification

The verification environment (testbenches, testcases, etc.) for the CV32E40X core can be found at core-v-verif. It is recommended that you start by reviewing the CORE-V Verification Strategy.

Contents

Getting Started with CV32E40X discusses the requirements and initial steps to start using CV32E40X.

Core Integration provides the instantiation template and gives descriptions of the design parameters as well as the input and output ports.

CV32E40X Pipeline described the overal pipeline structure.

The instruction and data interfaces of CV32E40X are explained in Instruction Fetch and Load-Store-Unit (LSU), respectively.

Physical Memory Attribution (PMA) describes the Physical Memory Attribution (PMA) unit.

The register-file is described in Register File.

eXtension Interface describes the custom eXtension interface.

Sleep Unit describes the Sleep unit.

The control and status registers are explained in Control and Status Registers.

Performance Counters gives an overview of the performance monitors and event counters available in CV32E40X.

Exceptions and Interrupts deals with the infrastructure for handling exceptions and interrupts.

Debug & Trigger gives a brief overview on the debug infrastructure.

RISC-V Formal Interface gives a brief overview of the RVFI module.

Glossary provides definitions of used terminology.

History

CV32E40X started its life as a fork of the CV32E40P from the OpenHW Group <https://www.openhwgroup.org>.

References

Contributors

Michael Gautschi (*gautschi@iis.ee.ethz.ch*)

Pasquale Davide Schiavone (*pschiavo@iis.ee.ethz.ch*)

Arjan Bink (*arjan.bink@silabs.com*)

Paul Zavalney (*paul.zavalney@silabs.com*)